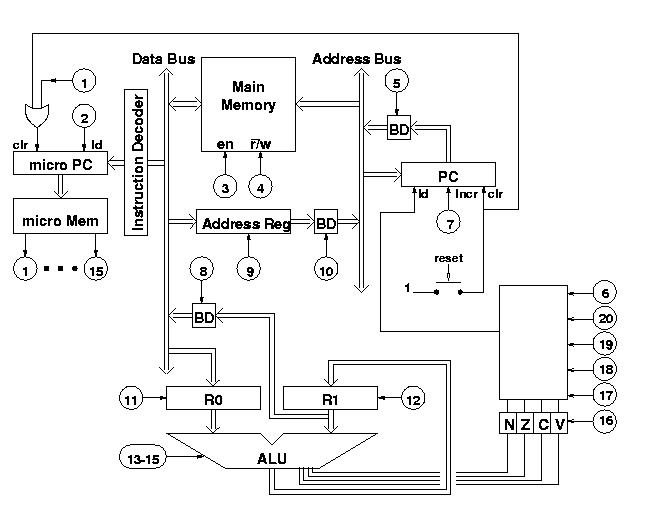

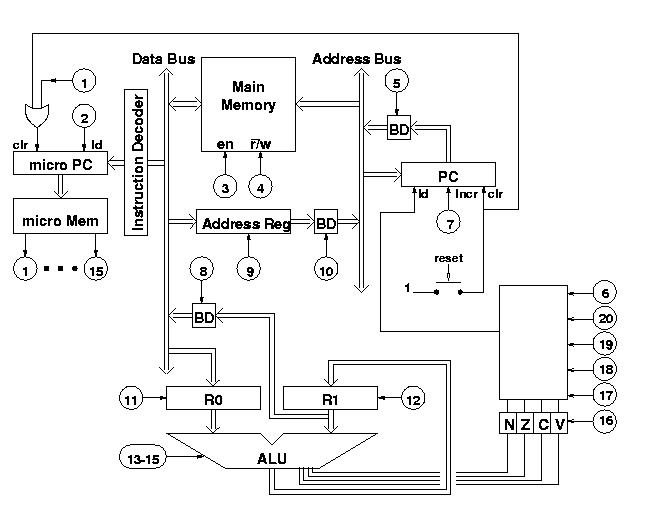

In fact the first computer does not even have the circuits necessary to implement such an instruction. First we need an additional register to hold information about the last operation computed by the ALU. This register is called the condition codes, usually abbreviated CC. The condition codes is a 4-bit register and the bits indicate respectively whether the value of the last operation was negative (the bit N), was zero (the bit Z), generated a carry (the bit C), or generated an overflow (the bit V). The CC register will be controled by another micro-operation which, when 1 will load the register with the information generated by the ALU. We could have used the same micro-operation as the one used to load R2 since these operations are currently used simultaneously. However, in the future, we might want to control them separately, for instance in order to write a comparison instruction. Such an instruction is identical to a subtract instruction, except that the result of the subtraction is not kept, only the condition codes. In addition to the condition codes, we we also need to control the ld signal of PC in more detail. This signal is currently 1 if and only if we generate the micro operation for unconditional jumps. It should now be generated by a more complicated circuit that generates 1 also when the micro memory has issued a jump zero micro operation and the Z bit is set, etc. Here is our modified computer:

For completeness, here is the (abbreviated) state table for the condition code register. The signals an, az, ac, and av are the outputs from the ALU:

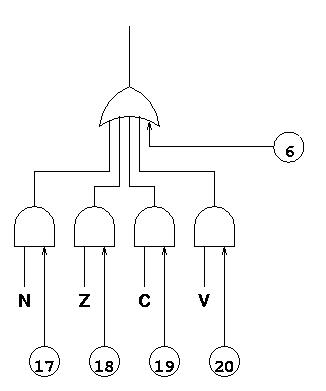

ld an az ac av N Z C V | N' Z' C' V' ----------------------------------------- 0 a b c d e f g h | e f g h 1 a b c d e f g h | a b c dAs you can see, it is an ordinary register. Now we must explain what is in the box that computes the ld signal of PC. It is a combinatorial circuit with 9 inputs, so the truth table will be quite large. It is much easier to show the circuit directly. Here it is:

As you can see, the output (the ld signal of PC) is 1 if either mop number 6 is one, or if both the bit N and mop number 17 are one, or if both the bit Z and mop number 18 are 1, or if both the bit C and mop number 19 are 1, or finally if both the bit V and mop number 20 are 1.

As mop 6 indicates unconditional jump, generating this mop automatically makes the ld signal of PC 1, so that PC is loaded with a new address just like before.

When we want to execute say a JN (jump if negative) instruction, we will emit mop number 17. If then at the same time, bit N is 1, PC will be loaded with the new value. If bit N is 0, PC will keep its old value, which is the address of the instruction immediately following the JN instruction and no jump will take place. A similar argument is valid for the Z, C, and V bits.

Now, we have to start thinking about the contents of the micro memory. First, since we have increased the number of mops from 15 to 20, we have to make the micro memory wider, adding these bits to existing instructions. The only thing we have to make sure is that mop 16 is generated at the same time as mop 12 so that the condition codes will be loaded at the same time as R1. Here is the modified contents of micro memory:

000000: 01101010000000000000 (fetch) 000001: 10000000000000000000 (NOP) 000010: 10101010001000000000 (LDIMM) 000011: 00101010100000000000 (LD) 000100: 10100000011000000000 (LD) 000101: 00101010100000000000 (ST) 000110: 00000001010000000000 (ST) 000111: 00010001010000000000 (ST) 001000: 00110001010000000000 (ST) 001001: 00010001010000000000 (ST) 001010: 10000001010000000000 (ST) 001011: 10000000000100010000 (COPY) 001100: 10000000000100110000 (SHL) 001101: 10000000000101010000 (SHR) 001110: 10000000000101110000 (ADD) 001111: 10000000000110010000 (SUB) 010000: 10000000000110110000 (AND) 010001: 10000000000111010000 (OR) 010010: 10000000000111110000 (NOT) 010011: 00101010100000000000 (JAL) 010100: 10000100010000000000 (JAL)Now we can start thinking of the implementation of the conditional jump instructions. In fact, they will be identical to the JAL instruction, except that where the JAL instruction uses MOP number 6, the JN instruction will use MOP 17, the JZ instruction will use MOP number 18, the JV instruction will use MOP number 19, and the JC instruction will use MOP number 20. Here is the contents of micro memory so far:

000000: 01101010000000000000 (fetch) 000001: 10000000000000000000 (NOP) 000010: 10101010001000000000 (LDIMM) 000011: 00101010100000000000 (LD) 000100: 10100000011000000000 (LD) 000101: 00101010100000000000 (ST) 000110: 00000001010000000000 (ST) 000111: 00010001010000000000 (ST) 001000: 00110001010000000000 (ST) 001001: 00010001010000000000 (ST) 001010: 10000001010000000000 (ST) 001011: 10000000000100010000 (COPY) 001100: 10000000000100110000 (SHL) 001101: 10000000000101010000 (SHR) 001110: 10000000000101110000 (ADD) 001111: 10000000000110010000 (SUB) 010000: 10000000000110110000 (AND) 010001: 10000000000111010000 (OR) 010010: 10000000000111110000 (NOT) 010011: 00101010100000000000 (JAL) 010100: 10000100010000000000 (JAL) 010101: 00101010100000000000 (JN) 010110: 10000000010000001000 (JN) 010111: 00101010100000000000 (JZ) 011000: 10000000010000000100 (JZ) 011001: 00101010100000000000 (JV) 011010: 10000000010000000010 (JV) 011011: 00101010100000000000 (JC) 011100: 10000000010000000001 (JC)